Materials, Manufacturing and Applications

Edited by Hagen Klauk

WILEY-VCH Verlag GmbH & Co. KGaA

Edited by Hagen Klauk

# **Related Titles**

Müllen, K., Scherf, U. (Eds.)

# **Organic Light Emitting Devices**

Synthesis, Properties and Applications

2006, ISBN 3-527-31218-8

Baltes, H., Brand, O., Fedder, G. K., Hierold, C., Korvink, J. G., Tabata, O. (Eds.)

# Enabling Technologies for MEMS and Nanodevices

**Advanced Micro and Nanosystems**

2004, ISBN 3-527-30746-X

Köhler, M., Fritzsche, W.

# Nanotechnology

An Introduction to Nanostructuring Techniques

2004, ISBN 3-527-30750-8

Roth, S., Carroll, D.

## **One-Dimensional Metals**

Conjugated Polymers, Organic Crystals, Carbon Nanotubes

2004. ISBN 3-527-30749-4

Pearce, T. C., Schiffman, S. S., Nagle, H. T., Gardner, J. W. (Eds.)

# Handbook of Machine Olfaction

**Electronic Nose Technology**

2003, ISBN 3-527-30358-8

Komiyama, M., Takeuchi, T., Mukawa, T., Asanuma, H.

# **Molecular Imprinting**

From Fundamentals to Applications

2003, ISBN 3-527-30569-6

Materials, Manufacturing and Applications

Edited by Hagen Klauk

WILEY-VCH Verlag GmbH & Co. KGaA

#### The Editor

Dr. Hagen Klauk Max Planck Institute for Solid State Research Heisenbergstr. 1 70569 Stuttgart Germany All books published by Wiley-VCH are carefully produced. Nevertheless, authors, editors, and publisher do not warrant the information contained in these books, including this book, to be free of errors. Readers are advised to keep in mind that statements, data, illustrations, procedural details or other items may inadvertently be inaccurate.

Library of Congress Card No.: applied for British Library Cataloguing-in-Publication Data A catalogue record for this book is available from the British Library.

# Bibliographic information published by Die Deutsche Bibliothek

Die Deutsche Bibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data is available in the Internet at \( http://dnb.ddb.de \).

© 2006 WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim

All rights reserved (including those of translation into other languages). No part of this book may be reproduced in any form – by photoprinting, microfilm, or any other means – nor transmitted or translated into a machine language without written permission from the publishers. Registered names, trademarks, etc. used in this book, even when not specifically marked as such, are not to be considered unprotected by law.

Typesetting Asco Typesetter, Hong Kong

Printing Strauss GmbH, Mörlenbach

Binding Schäffer GmbH, Grünstadt

Cover Design Grafik-Design Schulz,

Fußgönheim

Printed in the Federal Republic of Germany Printed on acid-free paper

**ISBN-13** 978-3-527-31264-1 **ISBN-10** 3-527-31264-1

# Contents

|       | Pretace XIII                                        |

|-------|-----------------------------------------------------|

|       | Author List XV                                      |

| I     | Introduction 1                                      |

| 1     | Organic Transistors 3                               |

|       | Gilles Horowitz                                     |

| 1.1   | Introduction 3                                      |

| 1.2   | Overview of the Organic Thin-film Transistor 4      |

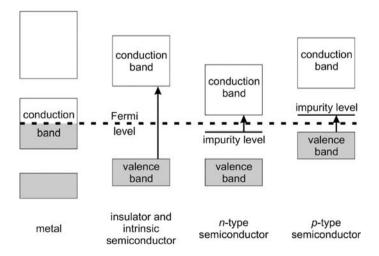

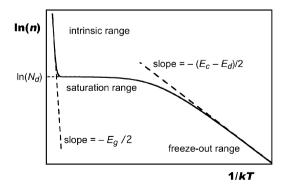

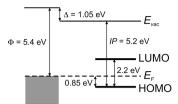

| 1.2.1 | Are Organic "Semiconductors" Real Semiconductors? 4 |

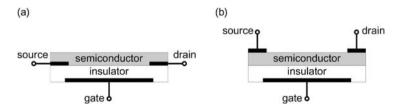

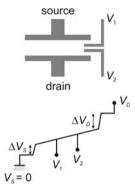

| 1.2.2 | Thin-film Transistor Architecture 7                 |

| 1.2.3 | Operating Mode 8                                    |

| 1.2.4 | Thickness of the Channel 10                         |

| 1.3   | Contact Resistance 15                               |

| 1.3.1 | Contact Resistance Extraction 15                    |

| 1.3.2 | Origin of Contact Resistance 19                     |

| 1.4   | Charge Transport 20                                 |

| 1.5   | Fabrication Techniques 21                           |

| 1.6   | The Materials 23                                    |

| 1.6.1 | Polymers 23                                         |

| 1.6.2 | Small Molecules 24                                  |

| 1.6.3 | n-Type Semiconductors 25                            |

| 1.6.4 | Single Crystals 26                                  |

| 1.6.5 | Insulators 27                                       |

| 1.7   | Concluding Remarks 28                               |

|       | Acknowledgements 29                                 |

|       | References 29                                       |

| II    | Advanced Materials for Organic Electronics 33               |

|-------|-------------------------------------------------------------|

| 2     | High-performance Pentacene Transistors 35                   |

| 2.1   | Tommie Kelley Introduction 35                               |

| 2.1   | Routes to Performance Improvement 38                        |

| 2.2.1 | Purification 38                                             |

| 2.2.1 | Device Evolution 39                                         |

| 2.2.3 | Structural Perfection 39                                    |

| 2.2.4 | Device Architecture 41                                      |

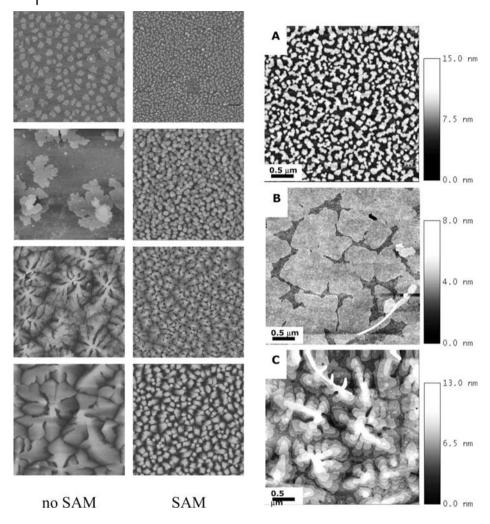

| 2.2.5 | Interfacial Control 45                                      |

| 2.3   | Structure–Property Relationships 48                         |

| 2.4   | Continuing Reports of High Mobilities 51                    |

| 2.5   | Performance in Practice 52                                  |

| 2.6   | The Future of High-performance Organic Transistors 53       |

|       | References 54                                               |

|       |                                                             |

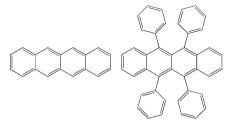

| 3     | Engineered Pentacenes 58                                    |

|       | John E. Anthony                                             |

| 3.1   | Introduction 58                                             |

| 3.2   | Reversible Functionalization 59                             |

| 3.3   | 2,3,9,10-Tetrasubstituted and 2,3-Disubstituted Pentacenes: |

|       | End-substituted Derivatives 60                              |

| 3.4   | Peri-functionalized Pentacene 63                            |

| 3.5   | Pentacene Functionalized at Both peri and End Positions 68  |

| 3.6   | Heteropentacenes 69                                         |

| 3.7   | Conclusion 72                                               |

|       | References 72                                               |

| 4     | Organic Semiconductors Based on Polythiophene and           |

| 7     | Indolo[3,2-b]carbazole 75                                   |

|       | Beng S. Ong, Yiliang Wu, and Yuning Li                      |

| 4.1   | Introduction 75                                             |

| 4.2   | Issues and Challenges 76                                    |

| 4.3   | Structural Considerations 79                                |

| 4.4   | Polythiophene Semiconductors 80                             |

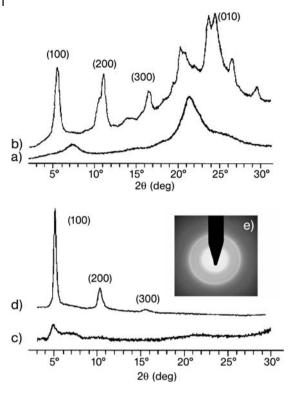

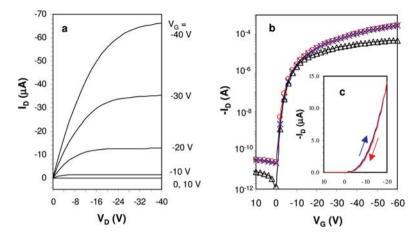

| 4.4.1 | High-performance Polythiophene Design 81                    |

| 4.4.2 | Polydialkylterthiophenes 82                                 |

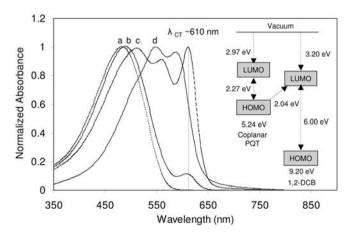

| 4.4.3 | Polydialkylquaterthiophenes 87                              |

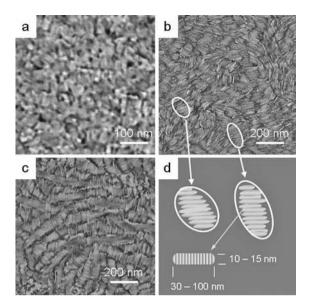

| 4.4.4 | Polythiophene Nanoparticles 90                              |

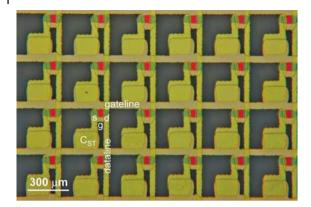

| 4.4.5 | Inkjet Patterned TFT Arrays 94                              |

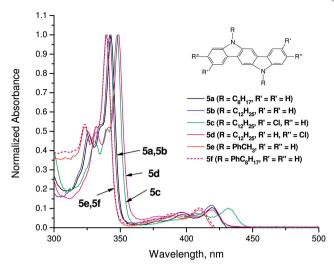

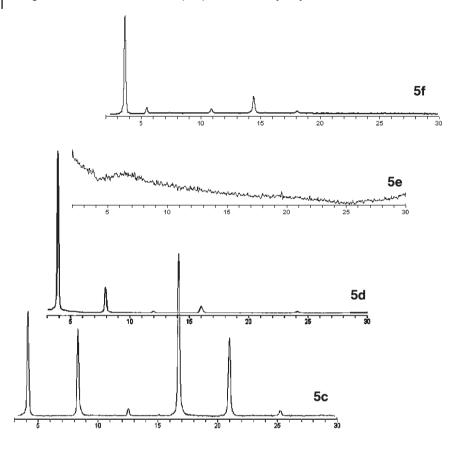

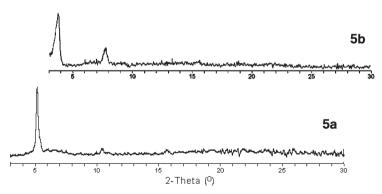

| 4.5   | Indocarbazole Designs 95                                    |

| 4.6   | Summary and Prospects 103                                   |

|       | Acknowledgements 105                                        |

|       | References 105                                              |

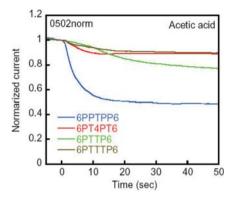

| 5       | Electrical and Environmental Stability of Polymer Thin-film Transistors 108 Alberto Salleo and Michael L. Chabinyc |

|---------|--------------------------------------------------------------------------------------------------------------------|

| 5.1     | Introduction 108                                                                                                   |

| 5.2     | Charge Trapping in TFTs 109                                                                                        |

| 5.2.1   | General Considerations 109                                                                                         |

| 5.2.2   | Bias Stress in Organic Transistors 111                                                                             |

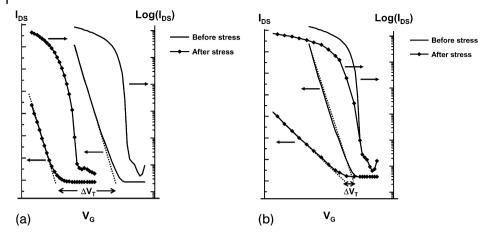

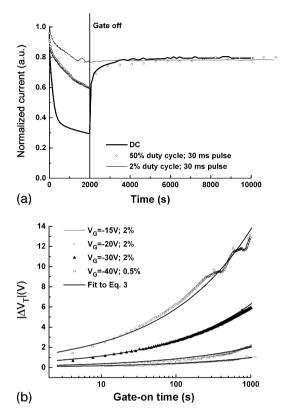

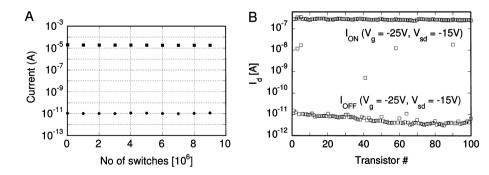

| 5.3     | Bias Stress in Polyfluorene and Polythiophene TFTs 112                                                             |

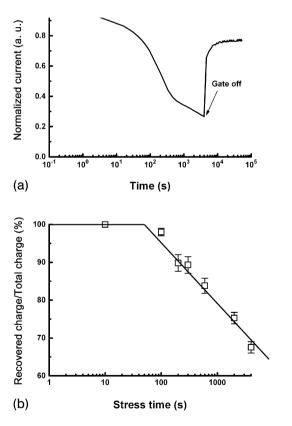

| 5.3.1   | Reversible Bias Stress 113                                                                                         |

| 5.3.2   | Long-lived Bias Stress 115                                                                                         |

| 5.3.3   | Dependence of Bias Stress on Operating Conditions; Lifetime                                                        |

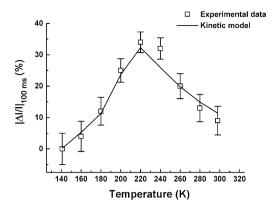

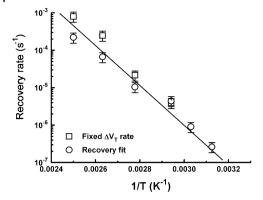

| E 2.4   | Predictions 116                                                                                                    |

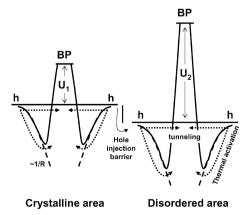

| 5.3.4   | A Microscopic Theory of Bias Stress 118                                                                            |

| 5.4     | Chemical Effects on Stability – Defects and Impurities 119                                                         |

| 5.4.1   | Introduction 119  Defeate in Malandar Structure 120                                                                |

| 5.4.2   | Defects in Molecular Structure 120                                                                                 |

| 5.4.2.1 | Defects from Synthesis 120                                                                                         |

| 5.4.2.2 | Photo-induced Defects 121                                                                                          |

| 5.4.3.1 | Thermochemical Analysis 123                                                                                        |

| 5.4.3.2 | Oxygen 124                                                                                                         |

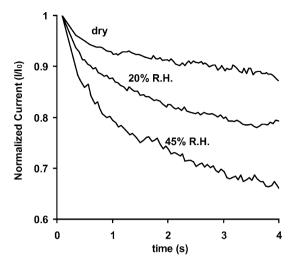

| 5.4.3.3 | Water 126                                                                                                          |

| 5.4.3.4 | Organic Solvents 127                                                                                               |

| 5.4.3.5 | Inorganic Impurities 127                                                                                           |

| 5.4.3   | Impurities 123                                                                                                     |

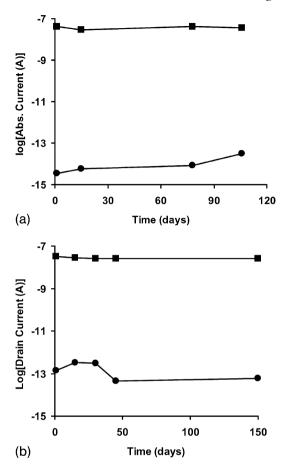

| 5.4.4   | Studies of TFT Lifetime 128                                                                                        |

| 5.5     | Conclusion 129                                                                                                     |

|         | Acknowledgments 129                                                                                                |

|         | References 129                                                                                                     |

| 6       | Gate Dielectrics 132                                                                                               |

|         | Marcus Halik                                                                                                       |

| 6.1     | Introduction 132                                                                                                   |

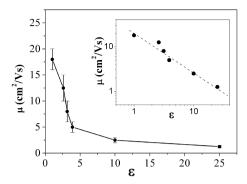

| 6.2     | The Impact of Gate Dielectrics on the Electrical Functionality of Organic TFTs 133                                 |

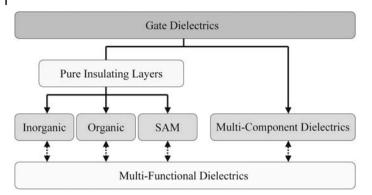

| 6.3     | Insulating Materials – An Overview 135                                                                             |

| 6.3.1   | Inorganic Gate Dielectrics 136                                                                                     |

| 6.3.2   | Polymer Gate Dielectrics 137                                                                                       |

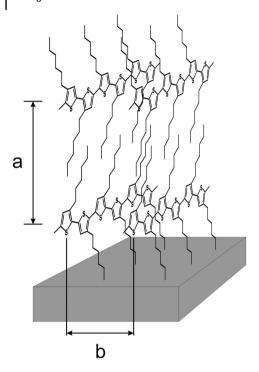

| 6.3.3   | Self-Assembled Monolayer Gate Dielectrics 138                                                                      |

| 6.3.4   | Multi-layer and Multi-component Gate Dielectrics 139                                                               |

| 6.3.5   | Multifunctional Dielectrics 140                                                                                    |

| 6.4     | Application-related Aspects of Dielectrics 140                                                                     |

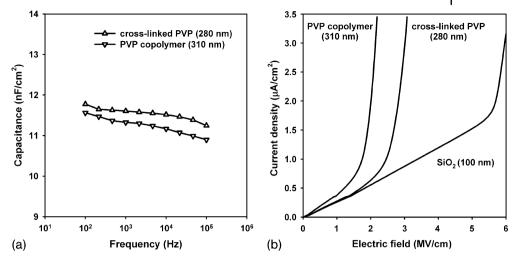

| 6.4.1   | Poly-4-vinylphenol Dielectrics 141                                                                                 |

| 6.4.2   | The Self-assembled Monolayer Approach 153                                                                          |

|         | References 161                                                                                                     |

| VIII                                    | Content    |

|-----------------------------------------|------------|

| * * * * * * * * * * * * * * * * * * * * | COTIVETIV. |

| vIII                                          | Contents |                                                         |

|-----------------------------------------------|----------|---------------------------------------------------------|

| ·                                             | 7        | Advanced Flexible Polymeric Substrates 163              |

|                                               |          | William A. MacDonald                                    |

|                                               | 7.1      | Introduction 163                                        |

|                                               | 7.2      | Polyester Substrates 163                                |

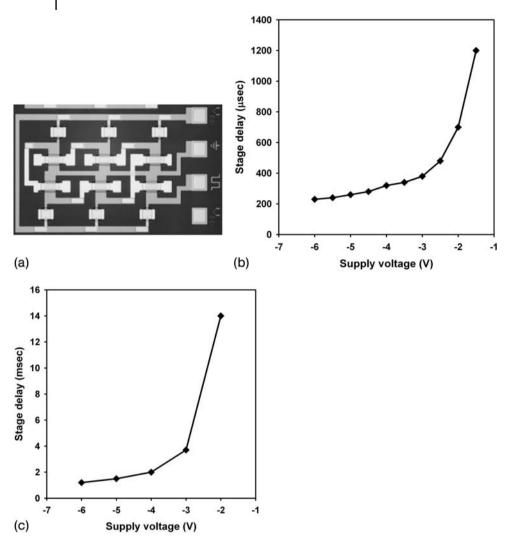

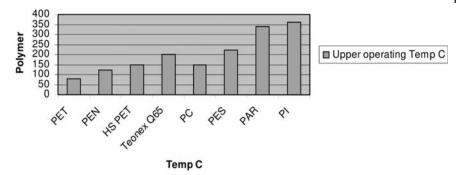

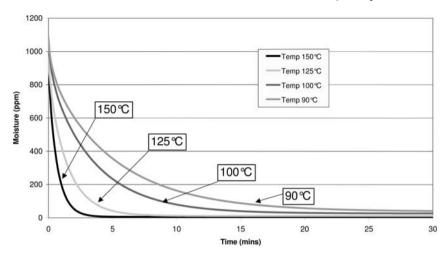

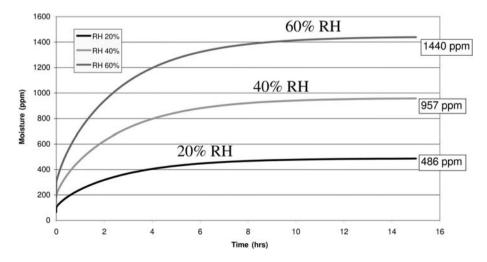

|                                               | 7.3      | Properties of Base Substrates 165                       |

|                                               | 7.3.1    | Optical Properties 165                                  |

|                                               | 7.3.2    | Birefringence 166                                       |

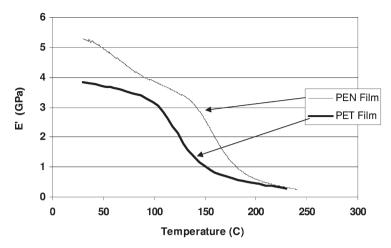

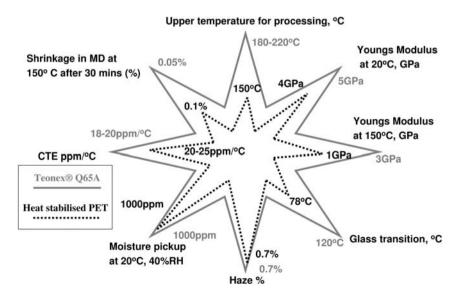

|                                               | 7.3.3    | Thermal Properties 166                                  |

|                                               | 7.3.4    | Solvent Resistance 167                                  |

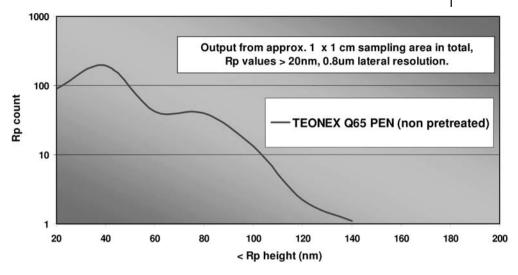

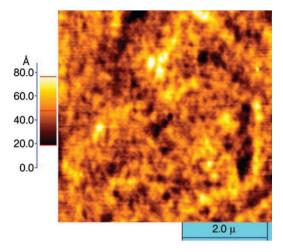

|                                               | 7.3.5    | Surface Quality 170                                     |

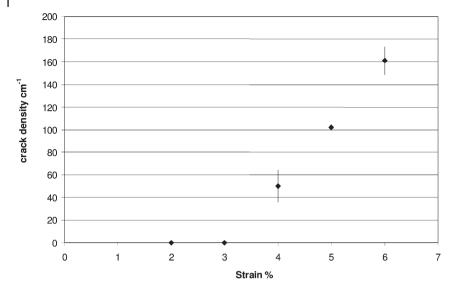

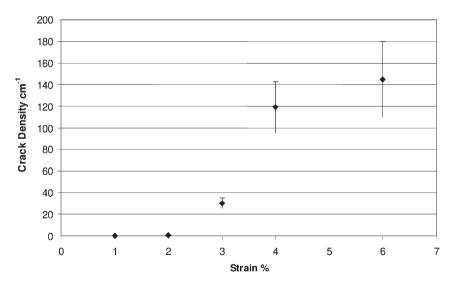

|                                               | 7.3.6    | Mechanical Properties 172                               |

|                                               | 7.3.7    | Summary of Key Properties of Base Substrates 173        |

|                                               | 7.4      | Multilayer Structures 174                               |

|                                               | 7.5      | Film in Application 177                                 |

|                                               |          | Acknowledgments 178                                     |

|                                               |          | References 178                                          |

| III Manufacturing for Organic Electronics 181 |          |                                                         |

|                                               | 8        | Reel-to-reel Vacuum Metallization 183                   |

|                                               |          | Roland Treutlein, Martin Bergsmann, and Carl J. Stonley |

|                                               | 8.1      | Reel-to-reel Vacuum Metallization 183                   |

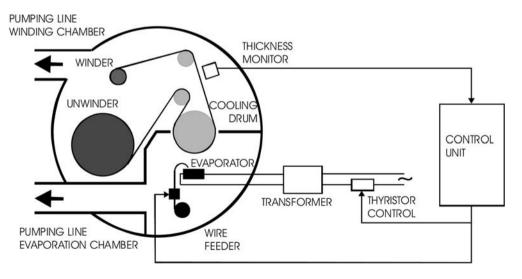

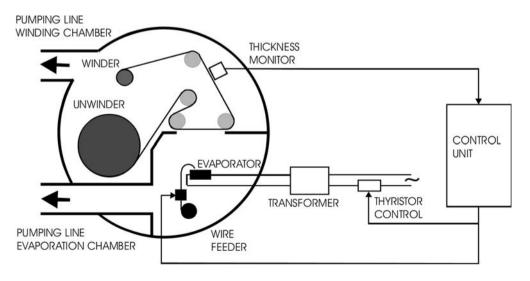

|                                               | 8.1.1    | The Metallization Process 184                           |

|                                               | 8.1.1.1  | Evaporation Sources 184                                 |

|                                               |          | Pretreatment and Cleaning of the Web Substrate 186      |

|                                               | 8.1.1.3  | PVD Process Flow 186                                    |

|                                               | 8.1.1.4  | Typical Process Times, Rates, and Quantities 189        |

|                                               | 8.1.1.5  | Transfer Metallization 190                              |

|                                               | 8.1.1.6  | Pattern-evaporated Layers 191                           |

|                                               | 8.1.2    | Properties of the Evaporated Layer 191                  |

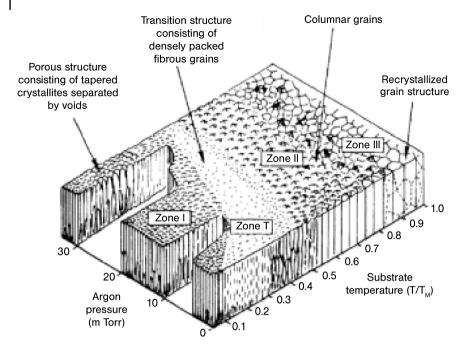

|                                               | 8.1.2.1  | Structure 191                                           |

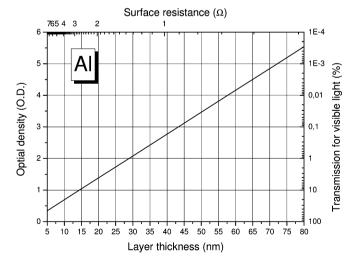

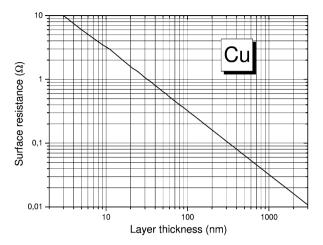

|                                               | 8.1.2.2  | Layer Thickness (Conductivity) 192                      |

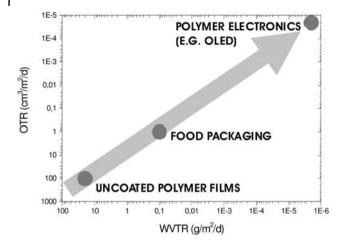

|                                               |          | Barrier 195                                             |

|                                               | 8.1.2.4  | Light Barrier 197                                       |

|                                               | 8.1.3    | Environmental Benefits of Vacuum Evaporated Layers 198  |

|                                               | 8.1.4    | Applications of Metallized Films 199                    |

|                                               | 8.1.4.1  | Barrier Packaging 199                                   |

|                                               | 8.1.4.2  | Decorative Applications 199                             |

|                                               | 8.1.4.3  | Functional Layers 199                                   |

|                                               | 8.1.4.4  | Polymer Electronic Substrates 200                       |

|                                               | 8.1.5    | Market Analysis 201                                     |

|                                               |          | References 202                                          |

| 9        | Organic Vapor Phase Deposition 203                                |

|----------|-------------------------------------------------------------------|

| ,        | Michael Heuken and Nico Meyer                                     |

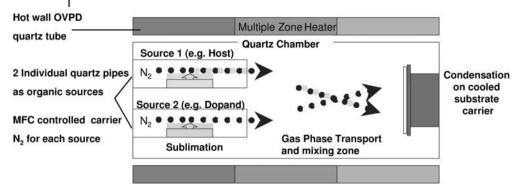

| 9.1      | Introduction 203                                                  |

| 9.1.1    | The Principle of OVPD 203                                         |

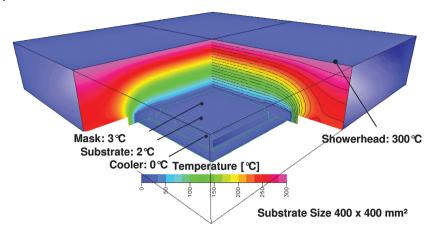

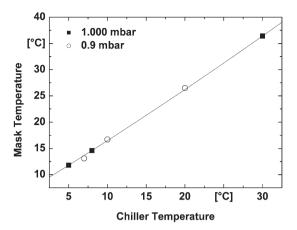

| 9.1.2    | Close Coupled Showerhead Technology 204                           |

| 9.2      | Deposition of Organic Thin Films 207                              |

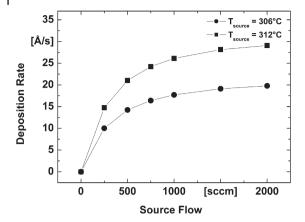

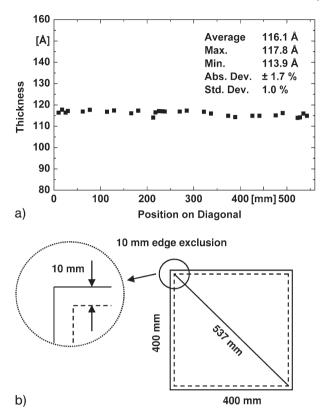

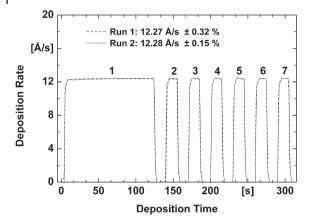

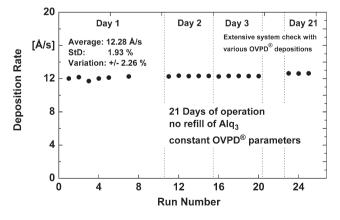

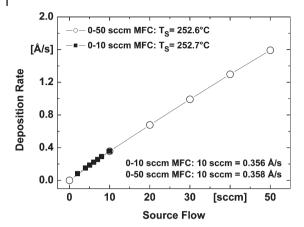

| 9.2.1    | Process Control in OVPD 207                                       |

| 9.2.2    | Co-deposition and Doping in OVPD 211                              |

| 9.2.3    | Controlled Morphology and Layer Interfaces in OVPD 213            |

| 9.3      | Electronic Devices by OVPD 215                                    |

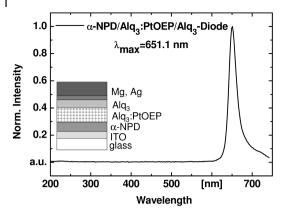

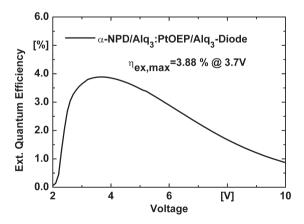

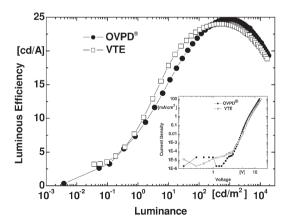

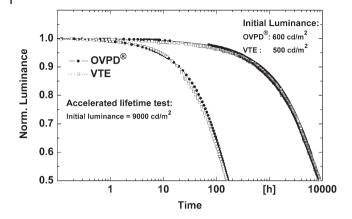

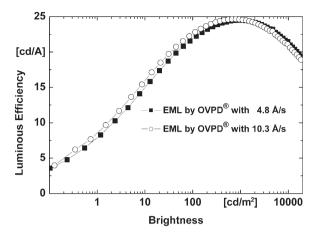

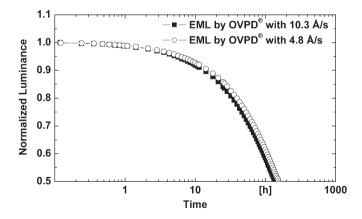

| 9.3.1    | OLEDs Made by OVPD 215                                            |

| 9.3.2    | Organic Photovoltaics by OVPD 220                                 |

| 9.3.3    | Organic Thin-film Transistors by OVPD 221                         |

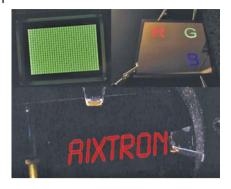

| 9.4      | Full-color OLED Displays 222                                      |

| 9.4.1    | Micropatterning by use of Shadow Masks 222                        |

| 9.4.2    | Mask-less Processes 224                                           |

| 9.5      | Material Properties of Organic Molecules for Use in OVPD 225      |

| 9.6      | Summary 226                                                       |

|          | Acknowledgment 229                                                |

|          | References 229                                                    |

|          |                                                                   |

| 10       | Thermal Imaging and Micro-contact Printing 233                    |

|          | Hee Hyun Lee, John Rogers, and Graciela Blanchet                  |

| 10.1     | Introduction 233                                                  |

| 10.2     | Building Blocks 233                                               |

| 10.3     | Printing and Patterning Techniques 235                            |

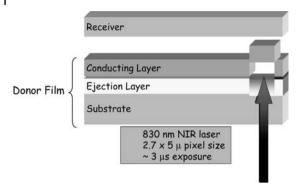

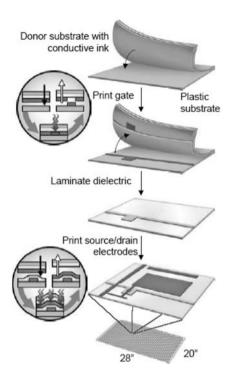

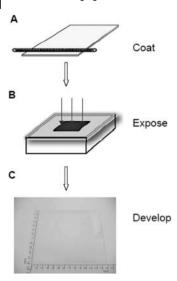

| 10.3.1   | Thermal Imaging 235                                               |

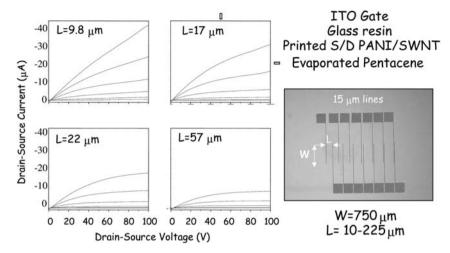

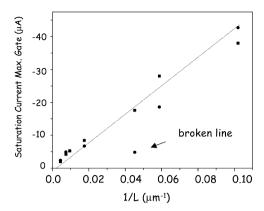

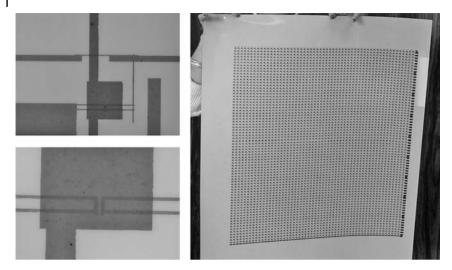

| 10.3.2   | Printed Devices: From TFTs to Large-area Backplanes 236           |

| 10.4     | Printable Materials 240                                           |

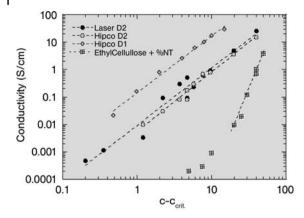

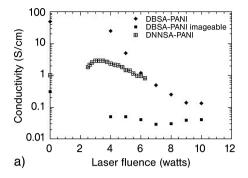

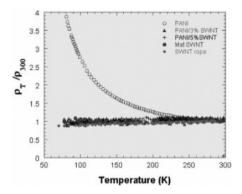

| 10.4.1   | Polyaniline Nanotube Composites: A High-resolution Printable      |

|          | Conductor 240                                                     |

| 10.5     | Micro-contact Printing 245                                        |

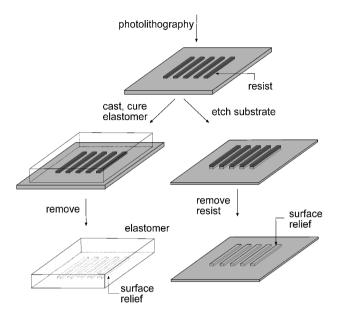

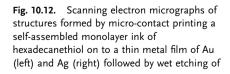

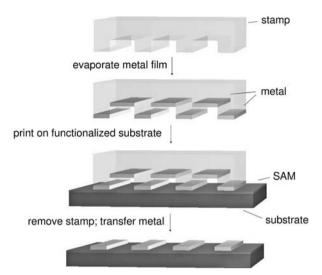

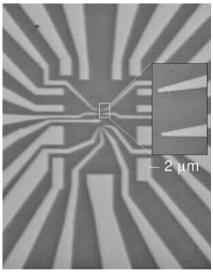

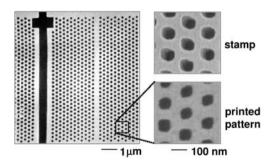

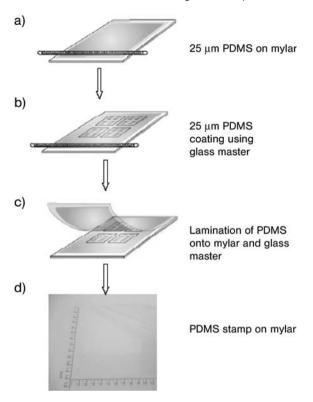

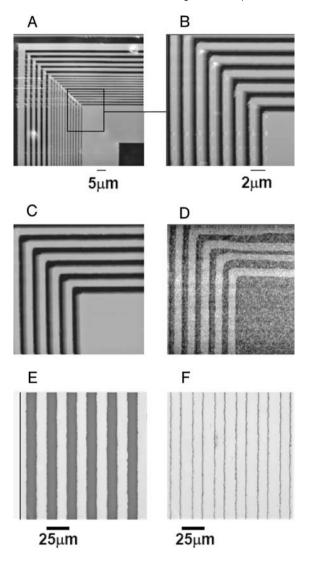

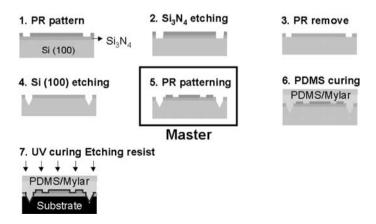

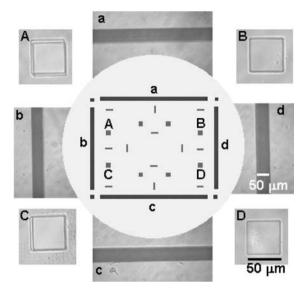

| 10.5.1   | Contact Printing with High-resolution Stamps 245                  |

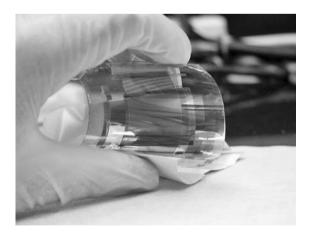

| 10.5.1.1 | High-resolution Stamps 246                                        |

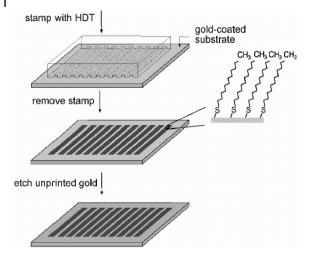

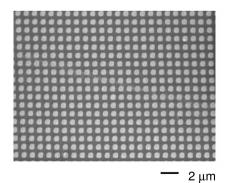

| 10.5.2   | Micro-contact Printing 247                                        |

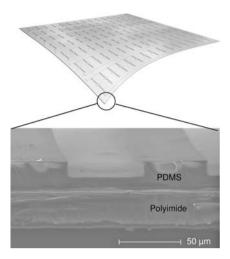

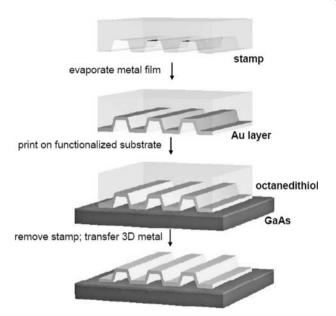

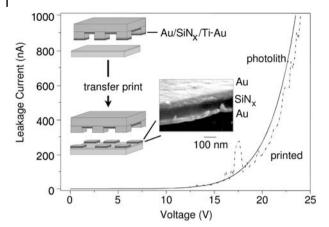

| 10.5.3   | Nanotransfer Printing 251                                         |

| 10.6     | Large Area Stamps, Molds, and Photomasks for Soft Lithography 259 |

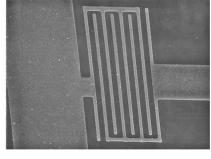

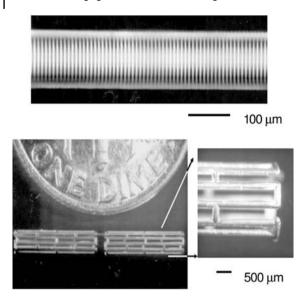

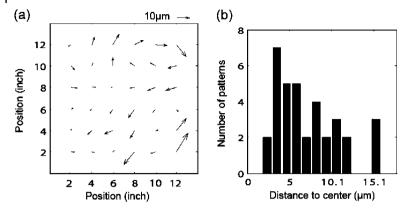

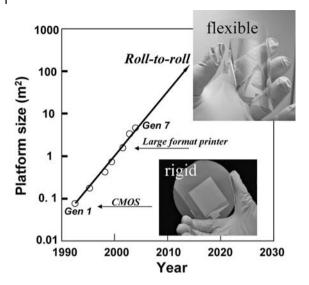

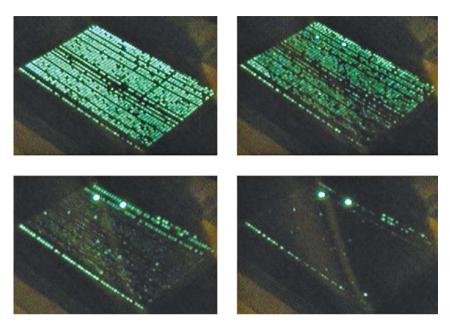

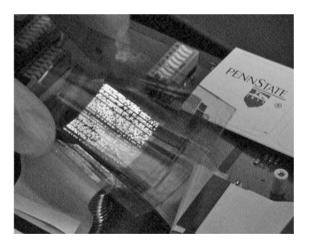

| 10.6.1   | Micro-contact Printing: A Path to Reel-to-reel Electronics 259    |

| 10.6.2   | Inexpensive Approaches to Large-area Printing 259                 |

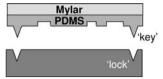

| 10.6.3   | Registration Using the Lock-and-key Mechanism in Soft             |

|          | Imprinting 264                                                    |

| 10.7     | Conclusions 266                                                   |

|          | Acknowledgments 268                                               |

|          | References 265                                                    |

| 11                                                             | Thin-film Transistor Fabrication by Digital Lithography 271 William S. Wong, Jürgen H. Daniel, Michael L. Chabinyc, Ana Claudia Arias, Steven E. Ready, and René Lujan                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.1                                                           | Introduction 271                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11.1                                                           | Jet-printed Patterning for Thin-film Transistor Processing 272                                                                                                                                                                                                                                                                                                                                                                                        |

| 11.2.1                                                         | Introduction 272                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11.2.1                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

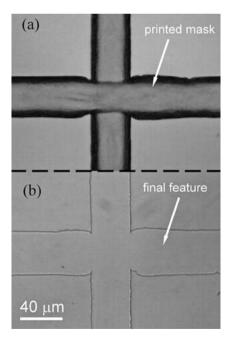

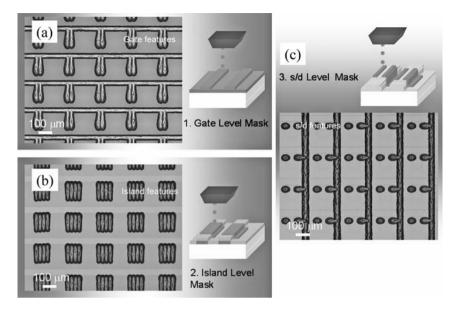

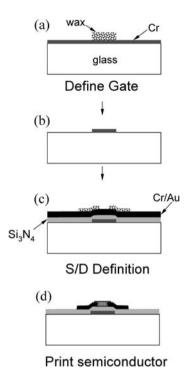

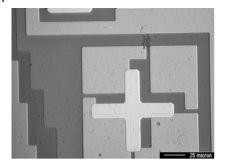

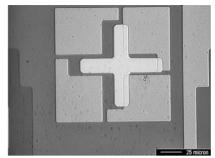

| 11.2.2                                                         | Jet-printed Phase-change Etch Masks 273 Digital Lithography 276                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                | 0 017                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

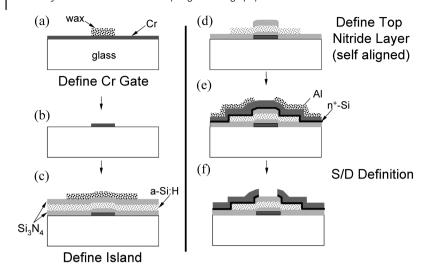

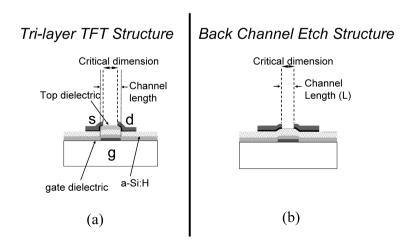

| 11.3.1<br>11.3.2                                               | Digital Lithography for TFT Device Fabrication 276 Thin-film Transistor Device Structures 277                                                                                                                                                                                                                                                                                                                                                         |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                | Amorphous Silicon TFTs 277                                                                                                                                                                                                                                                                                                                                                                                                                            |

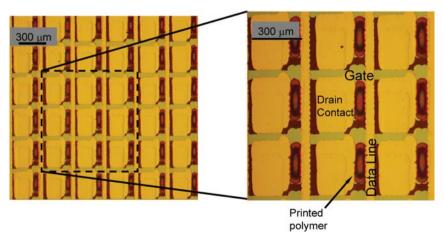

|                                                                | Polymeric TFTs by Digital Lithography 279  This Class Townish of Posics Class to initial 282                                                                                                                                                                                                                                                                                                                                                          |

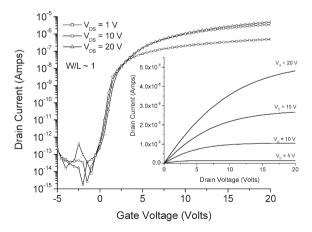

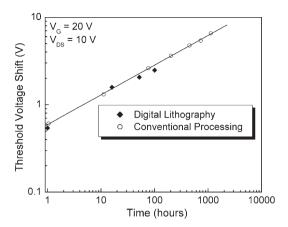

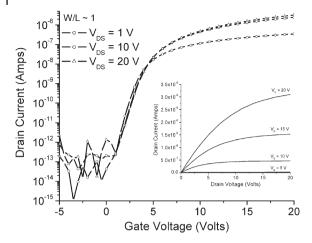

| 11.3.3                                                         | Thin-film Transistor Device Characteristics 282                                                                                                                                                                                                                                                                                                                                                                                                       |

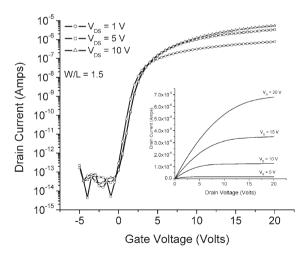

|                                                                | a-Si:H TFTs 282                                                                                                                                                                                                                                                                                                                                                                                                                                       |

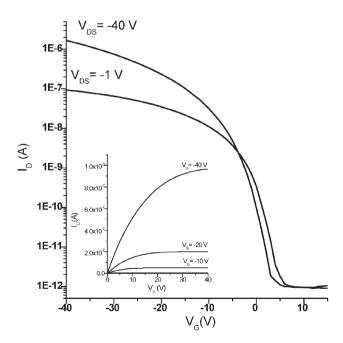

|                                                                | Printed Polymeric TFTs 284                                                                                                                                                                                                                                                                                                                                                                                                                            |

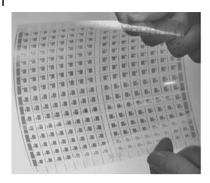

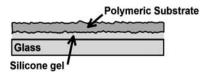

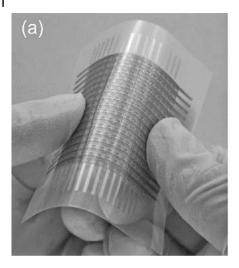

| 11.4                                                           | TFTs on Flexible Substrates 285                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11.4.1                                                         | Introduction 285                                                                                                                                                                                                                                                                                                                                                                                                                                      |

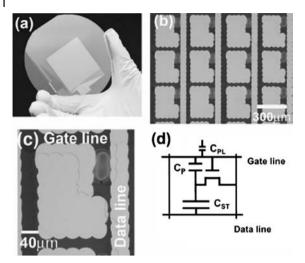

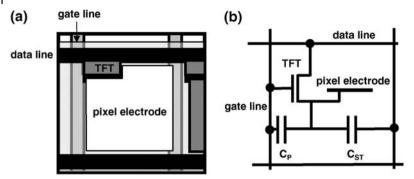

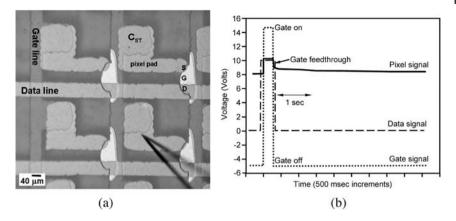

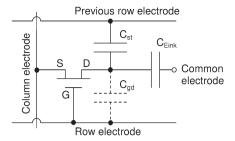

| 11.4.2                                                         | TFT Pixel Design Considerations 285                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11.4.3                                                         | Digital Lithography for Flexible Backplanes 287                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11.5                                                           | Display Applications with Print-patterned Backplanes 290                                                                                                                                                                                                                                                                                                                                                                                              |

| 11.6                                                           | Conclusions 291                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                | Acknowledgments 291                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                | References 291                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 12                                                             | Manufacturing of Organic Transistor Circuits by Solution-based Printing 29-                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                | Henning Sirringhaus, Christoph W. Sele, Timothy von Werne, and                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                | Catherine Ramsdale                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12.1                                                           | Introduction to Printed Organic Thin Film Transistors 294                                                                                                                                                                                                                                                                                                                                                                                             |

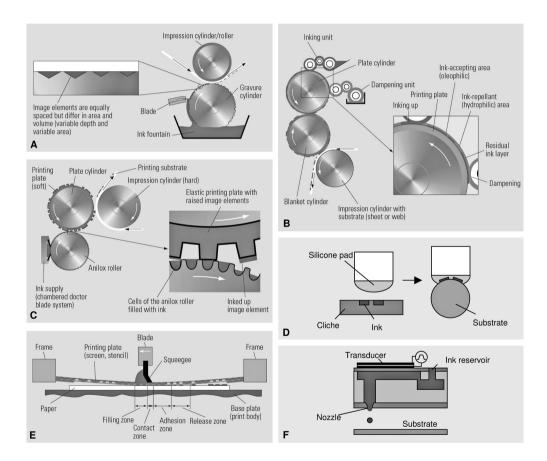

| 12.2                                                           | Overview of Printing-based Manufacturing Approaches for OTFTs 297                                                                                                                                                                                                                                                                                                                                                                                     |

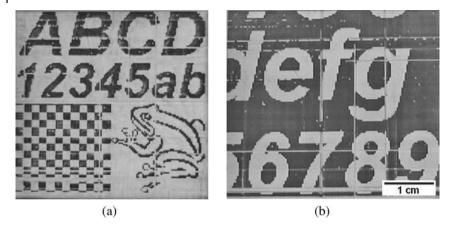

| 12.2.1                                                         | Screen Printing 298                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12.2.2                                                         | Offset Printing 299                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12.2.3                                                         | Offset I finding 277                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12.2.4                                                         | Gravure Printing 300                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12.2.1                                                         | Gravure Printing 300 Elevography 300                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1225                                                           | Flexography 300                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12.2.5                                                         | Flexography 300<br>Inkjet Printing 301                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12.2.6                                                         | Flexography 300 Inkjet Printing 301 Laser-based Dry-printing Techniques 302                                                                                                                                                                                                                                                                                                                                                                           |

| 12.2.6<br>12.2.7                                               | Flexography 300 Inkjet Printing 301 Laser-based Dry-printing Techniques 302 Other Nonlithographic Manufacturing Approaches 302                                                                                                                                                                                                                                                                                                                        |

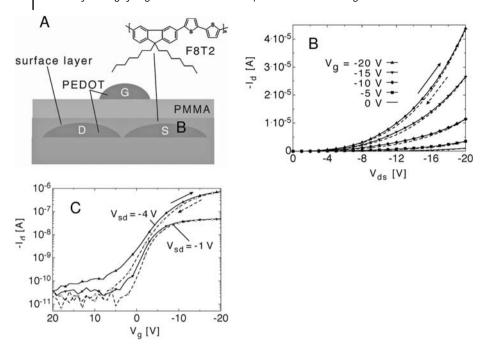

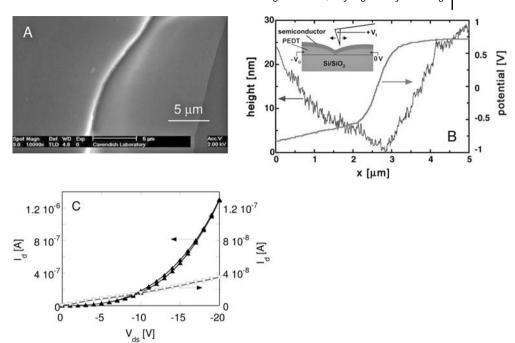

| 12.2.6<br>12.2.7<br>12.3                                       | Flexography 300 Inkjet Printing 301 Laser-based Dry-printing Techniques 302 Other Nonlithographic Manufacturing Approaches 302 High-resolution, Self-aligned Inkjet Printing 304                                                                                                                                                                                                                                                                      |

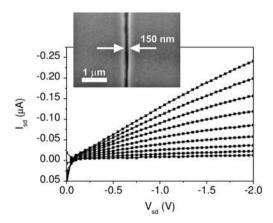

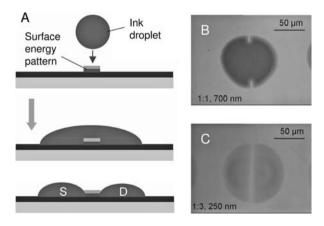

| 12.2.6<br>12.2.7<br>12.3<br>12.3.1                             | Flexography 300 Inkjet Printing 301 Laser-based Dry-printing Techniques 302 Other Nonlithographic Manufacturing Approaches 302 High-resolution, Self-aligned Inkjet Printing 304 Self-aligned Printing by Selective Surface Treatment 305                                                                                                                                                                                                             |

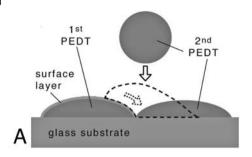

| 12.2.6<br>12.2.7<br>12.3<br>12.3.1<br>12.3.2                   | Flexography 300 Inkjet Printing 301 Laser-based Dry-printing Techniques 302 Other Nonlithographic Manufacturing Approaches 302 High-resolution, Self-aligned Inkjet Printing 304 Self-aligned Printing by Selective Surface Treatment 305 Self-aligned Printing by Surface Segregation 307                                                                                                                                                            |

| 12.2.6<br>12.2.7<br>12.3<br>12.3.1<br>12.3.2<br>12.3.3         | Flexography 300 Inkjet Printing 301 Laser-based Dry-printing Techniques 302 Other Nonlithographic Manufacturing Approaches 302 High-resolution, Self-aligned Inkjet Printing 304 Self-aligned Printing by Selective Surface Treatment 305 Self-aligned Printing by Surface Segregation 307 Self-aligned Printing by Autophobing 308                                                                                                                   |

| 12.2.6<br>12.2.7<br>12.3<br>12.3.1<br>12.3.2                   | Flexography 300 Inkjet Printing 301 Laser-based Dry-printing Techniques 302 Other Nonlithographic Manufacturing Approaches 302 High-resolution, Self-aligned Inkjet Printing 304 Self-aligned Printing by Selective Surface Treatment 305 Self-aligned Printing by Surface Segregation 307 Self-aligned Printing by Autophobing 308 Performance and Reliability of Solution-processed OTFTs for                                                       |

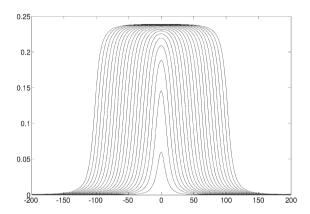

| 12.2.6<br>12.2.7<br>12.3<br>12.3.1<br>12.3.2<br>12.3.3<br>12.4 | Flexography 300 Inkjet Printing 301 Laser-based Dry-printing Techniques 302 Other Nonlithographic Manufacturing Approaches 302 High-resolution, Self-aligned Inkjet Printing 304 Self-aligned Printing by Selective Surface Treatment 305 Self-aligned Printing by Surface Segregation 307 Self-aligned Printing by Autophobing 308 Performance and Reliability of Solution-processed OTFTs for Applications in Flexible Displays 314                 |

| 12.2.6<br>12.2.7<br>12.3<br>12.3.1<br>12.3.2<br>12.3.3         | Flexography 300 Inkjet Printing 301 Laser-based Dry-printing Techniques 302 Other Nonlithographic Manufacturing Approaches 302 High-resolution, Self-aligned Inkjet Printing 304 Self-aligned Printing by Selective Surface Treatment 305 Self-aligned Printing by Surface Segregation 307 Self-aligned Printing by Autophobing 308 Performance and Reliability of Solution-processed OTFTs for Applications in Flexible Displays 314 Conclusions 318 |

| 12.2.6<br>12.2.7<br>12.3<br>12.3.1<br>12.3.2<br>12.3.3<br>12.4 | Flexography 300 Inkjet Printing 301 Laser-based Dry-printing Techniques 302 Other Nonlithographic Manufacturing Approaches 302 High-resolution, Self-aligned Inkjet Printing 304 Self-aligned Printing by Selective Surface Treatment 305 Self-aligned Printing by Surface Segregation 307 Self-aligned Printing by Autophobing 308 Performance and Reliability of Solution-processed OTFTs for Applications in Flexible Displays 314                 |

| IV     | Devices, Applications, and Products 323                                                                                                                                                                              |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13     | From Transistors to Large-scale Integrated Circuits 325 Gerwin H. Gelinck, Erik van Veenendaal, Eduard J. Meijer, Eugenio Cantatore, H. Edzer A. Huitema, Pieter van Lieshout, Fred J. Touwslager, Alwin W. Marsman, |

|        | and Dago M. de Leeuw                                                                                                                                                                                                 |

| 13.1   | Introduction 325                                                                                                                                                                                                     |

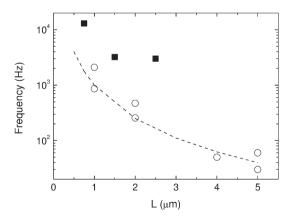

| 13.2   | Discrete Devices 326                                                                                                                                                                                                 |

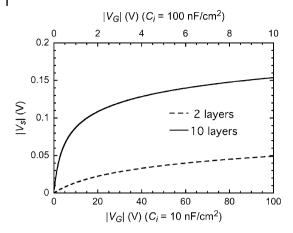

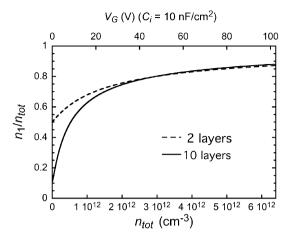

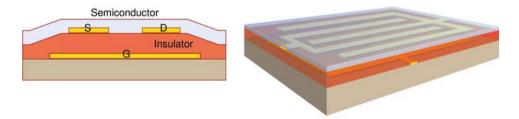

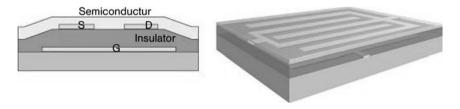

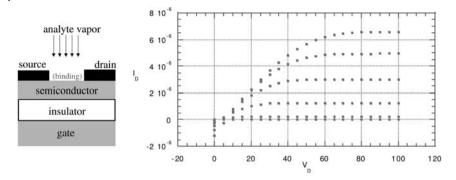

| 13.2.1 | Basic Device Operation of Organic Transistor 326                                                                                                                                                                     |

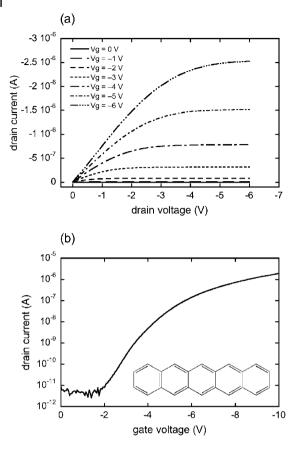

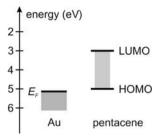

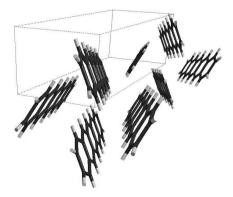

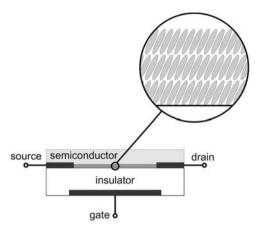

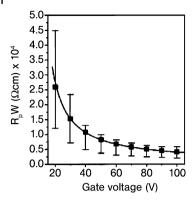

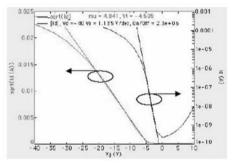

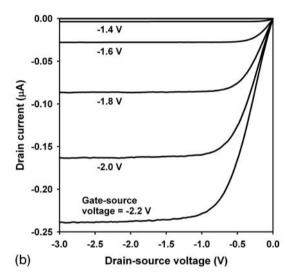

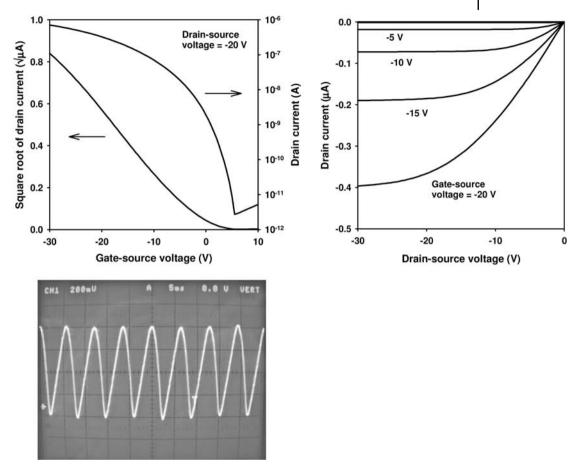

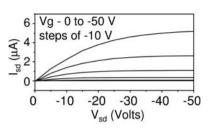

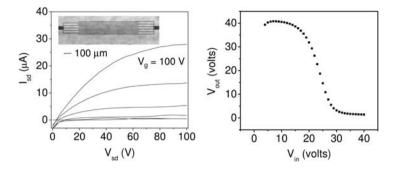

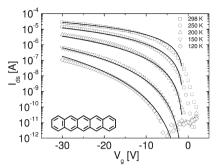

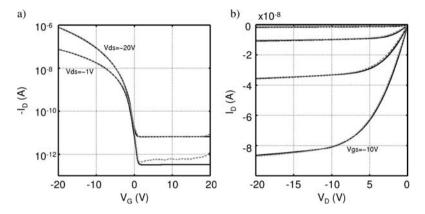

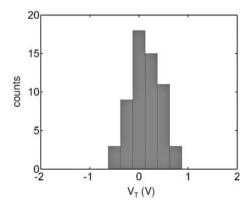

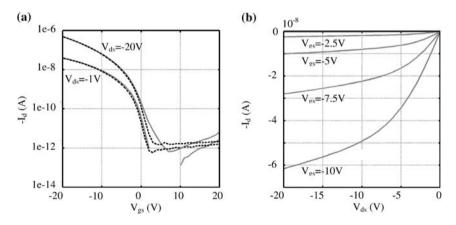

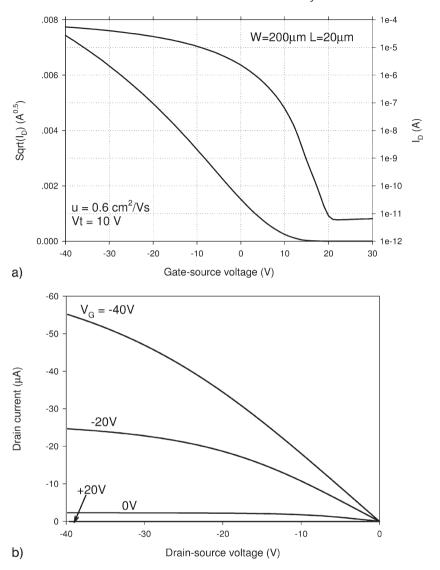

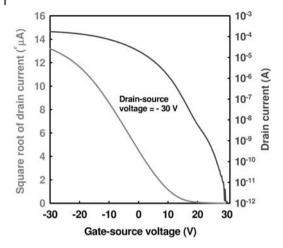

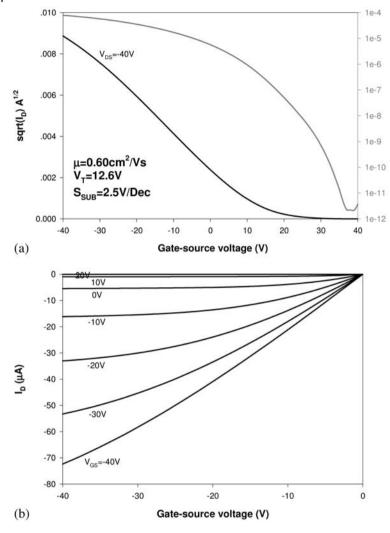

| 13.2.2 | Current-Voltage Characteristics 327                                                                                                                                                                                  |

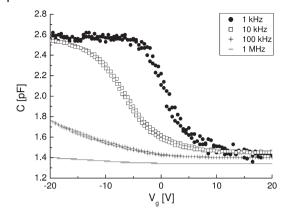

| 13.2.3 | Capacitance–Voltage Characteristics 328                                                                                                                                                                              |

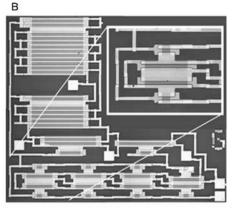

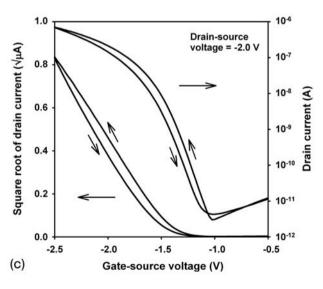

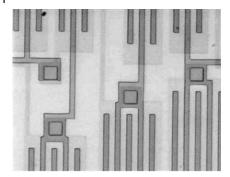

| 13.3   | Fabrication and Characterization of Integrated Circuits 330                                                                                                                                                          |

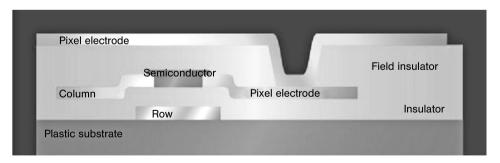

| 13.3.1 | Fabrication 331                                                                                                                                                                                                      |

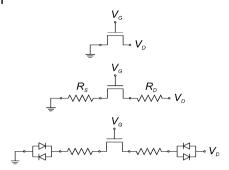

| 13.3.2 | Modeling 333                                                                                                                                                                                                         |

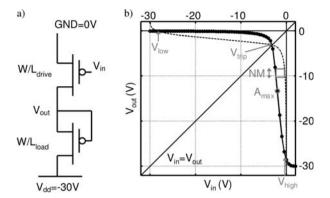

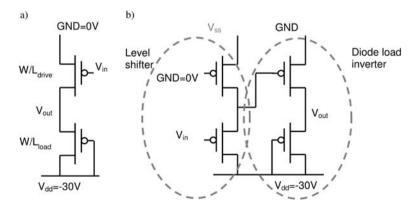

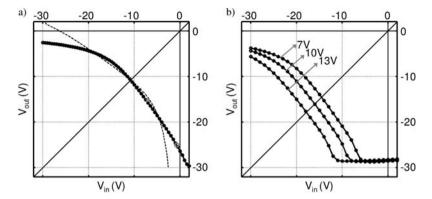

| 13.3.3 | Analysis of Inverters 336                                                                                                                                                                                            |

| 13.3.4 | Analysis of Integrated Circuits 340                                                                                                                                                                                  |

|        | Acknowledgments 342                                                                                                                                                                                                  |

|        | References 342                                                                                                                                                                                                       |

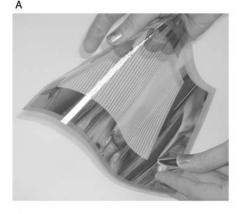

| 14     | Roll-up Active-matrix Displays 344                                                                                                                                                                                   |

|        | H. Edzer A. Huitema, Gerwin H. Gelinck, Erik van Veenendaal, Fred J. Touwslager,                                                                                                                                     |

|        | and Pieter J. G. van Lieshout                                                                                                                                                                                        |

| 14.1   | Introduction 344                                                                                                                                                                                                     |

| 14.1.1 | Non-rigid Display Research and Development Overview 345                                                                                                                                                              |

| 14.2   | Rollable Active-matrix Backplane Technology 346                                                                                                                                                                      |

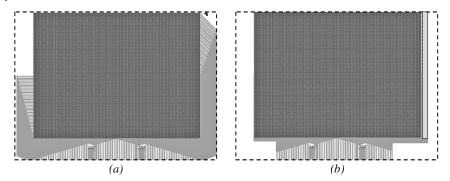

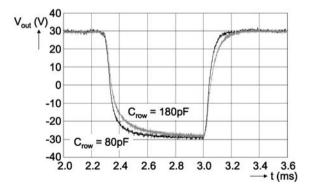

| 14.3   | Roll-up Active-matrix Backplane Design 349                                                                                                                                                                           |

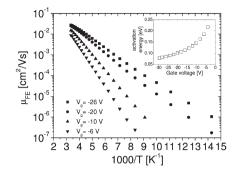

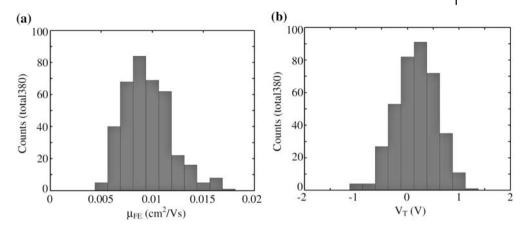

| 14.3.1 | Field-effect Mobility Effects 351                                                                                                                                                                                    |

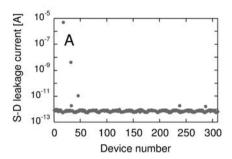

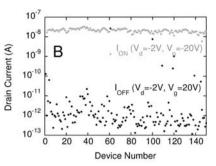

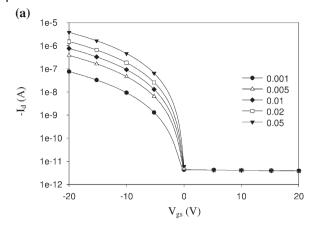

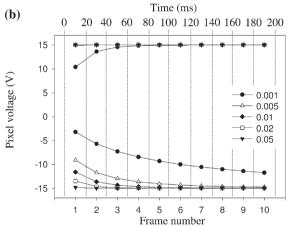

| 14.3.2 | Leakage Current Effects 353                                                                                                                                                                                          |

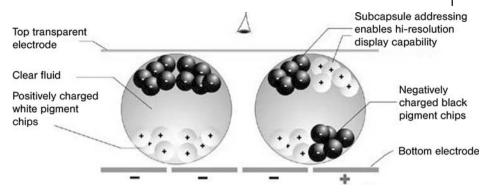

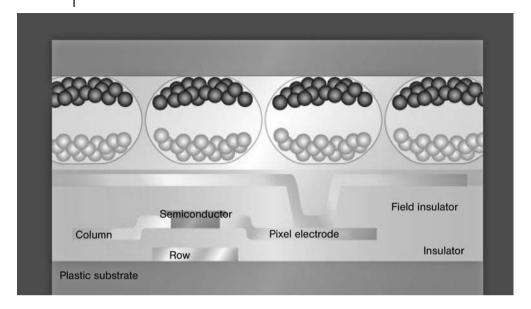

| 14.4   | The Electronic Ink Film 354                                                                                                                                                                                          |

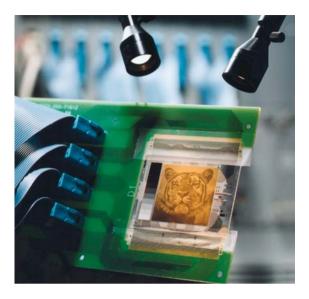

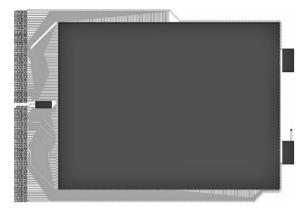

| 14.5   | Roll-up Display Integration 355                                                                                                                                                                                      |

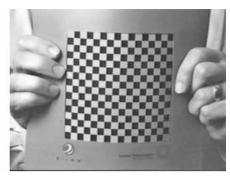

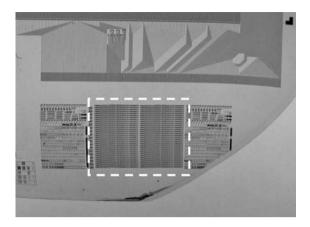

| 14.6   | Functional Active-matrix Roll-up Displays 355                                                                                                                                                                        |

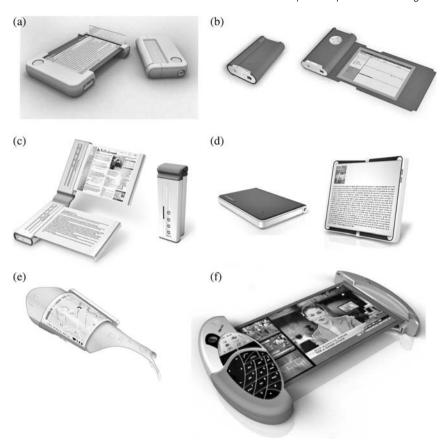

| 14.7   | Roll-up Display Device Concepts 358                                                                                                                                                                                  |

| 14.8   | Towards a System-on-plastic: Driver Integration 358                                                                                                                                                                  |

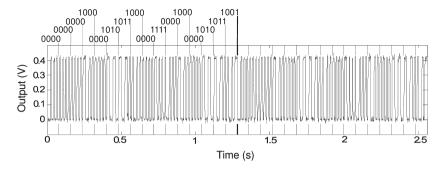

| 14.8.1 | Row Driver Integration 358                                                                                                                                                                                           |

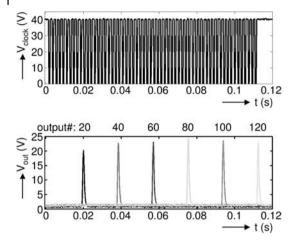

| 14.8.2 | Stand-alone Shift Registers 360                                                                                                                                                                                      |

| 14.8.3 | Integrated Shift Registers 362                                                                                                                                                                                       |

|        | Acknowledgment 364                                                                                                                                                                                                   |

|        | References 364                                                                                                                                                                                                       |

| 15     | Active-matrix Light-emitting Displays 367                                                                                                                                                                            |

|        | Shelby F. Nelson and Lisong Zhou                                                                                                                                                                                     |

| 15.1   | Introduction 367                                                                                                                                                                                                     |

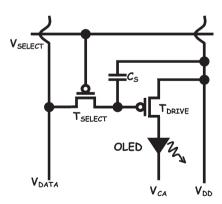

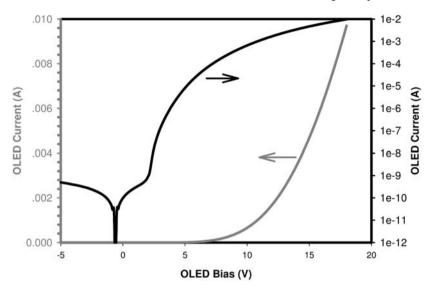

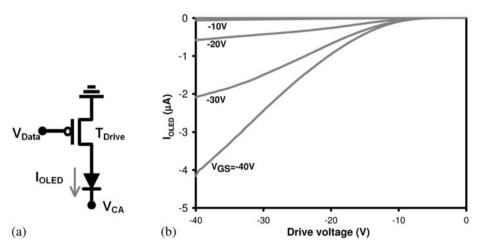

| 15.2   | OLED Pixel Differences from LCDs 369                                                                                                                                                                                 |

| 15.3   | Complex Pixel Design 369                                                                                                                                                                                             |

| 15.4   | Practical Design 370                                                                                                                                                                                                 |

| XII | Contents                              |                                                                                                                                                                                                                                                                          |

|-----|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

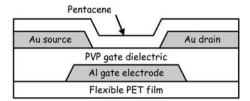

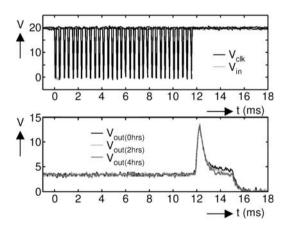

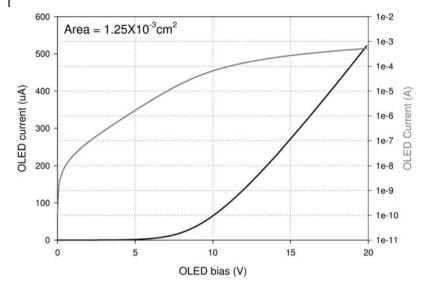

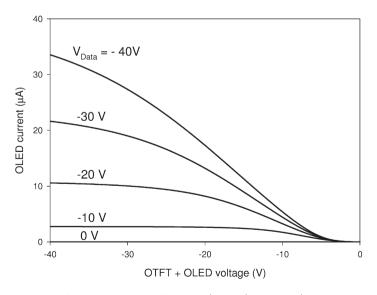

|     | 15.5                                  | AIM-SPICE Simulation of Pentacene TFT-driven OLEDs 372                                                                                                                                                                                                                   |

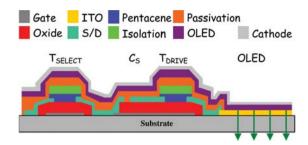

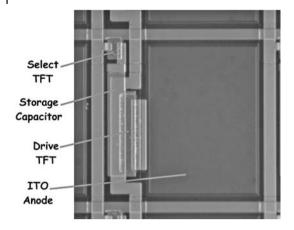

|     | 15.6                                  | Fabrication Process 375                                                                                                                                                                                                                                                  |

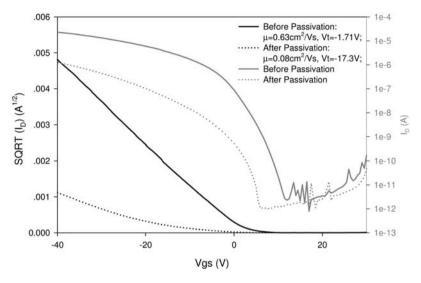

|     | 15.7                                  | Device Passivation 376                                                                                                                                                                                                                                                   |

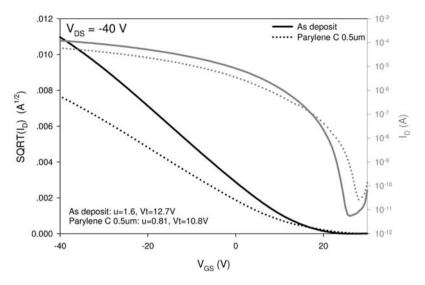

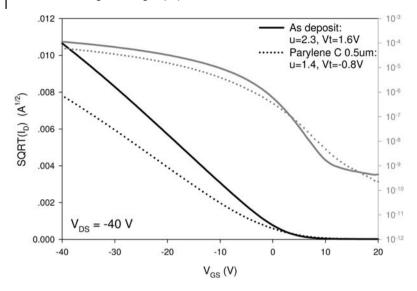

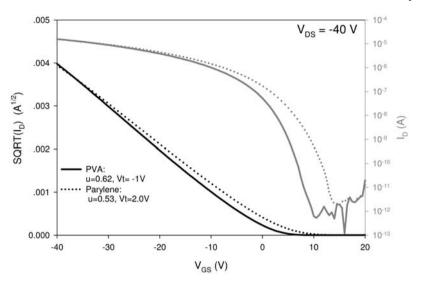

|     | 15.8                                  | PVA and Parylene 380                                                                                                                                                                                                                                                     |

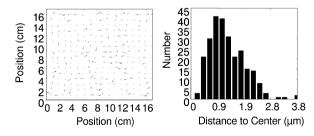

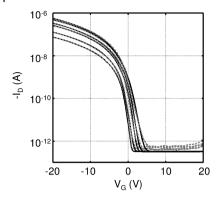

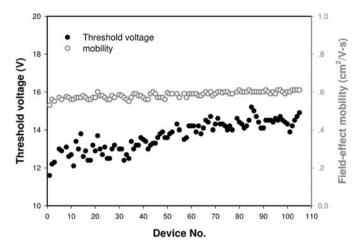

|     | 15.9                                  | Pentacene TFT Uniformity 381                                                                                                                                                                                                                                             |

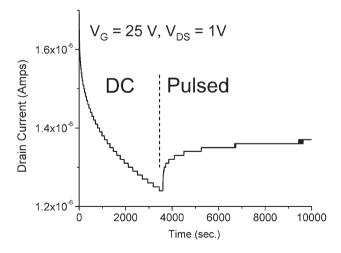

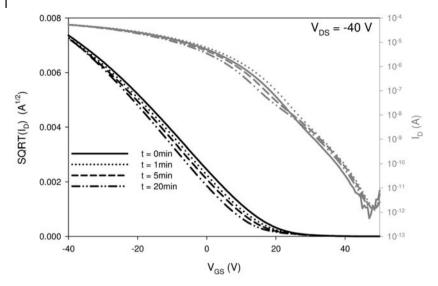

|     | 15.10                                 | Stability 383                                                                                                                                                                                                                                                            |

|     | 15.11                                 | Integration of TFTs and OLEDs 384                                                                                                                                                                                                                                        |

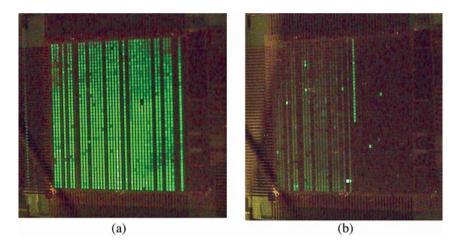

|     | 15.12                                 | Flexible OLED Display 386                                                                                                                                                                                                                                                |

|     | 15.13                                 | Substrate Selection and Mounting 387                                                                                                                                                                                                                                     |

|     | 15.14                                 | Thermal Dimensional Stability 387                                                                                                                                                                                                                                        |

|     | 15.15                                 | Surface Quality 388                                                                                                                                                                                                                                                      |

|     | 15.16                                 | Chemical Resistance 389                                                                                                                                                                                                                                                  |

|     | 15.17                                 | Fabrication Process 390                                                                                                                                                                                                                                                  |

|     | 15.18                                 | Display Results 390                                                                                                                                                                                                                                                      |

|     | 15.19                                 | Conclusion 391                                                                                                                                                                                                                                                           |

|     |                                       | References 392                                                                                                                                                                                                                                                           |

|     | 16                                    | Large-area Detectors and Sensors 395                                                                                                                                                                                                                                     |

|     | 161                                   | Takao Someya and Takayasu Sakurai                                                                                                                                                                                                                                        |

|     | 16.1                                  | Introduction 395                                                                                                                                                                                                                                                         |

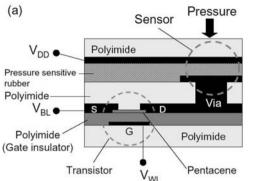

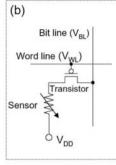

|     | 16.2                                  | Large-area Pressure Sensors 396                                                                                                                                                                                                                                          |

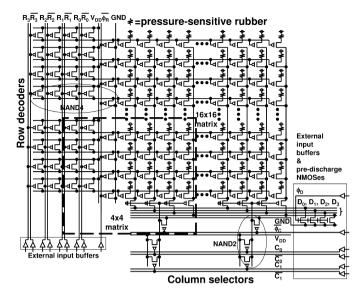

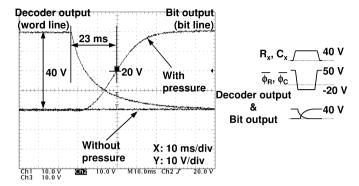

|     | 16.3                                  | Organic Transistor-based Integrated Circuits 398                                                                                                                                                                                                                         |

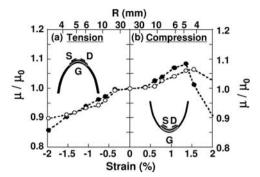

|     | 16.4                                  | Bending Experiments of Organic Transistors 400                                                                                                                                                                                                                           |

|     |                                       |                                                                                                                                                                                                                                                                          |

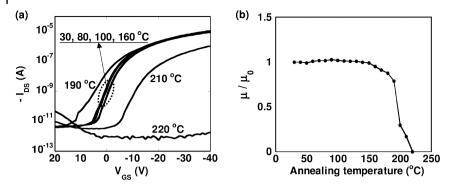

|     | 16.5                                  | High-temperature Operation of Organic Transistors 401                                                                                                                                                                                                                    |

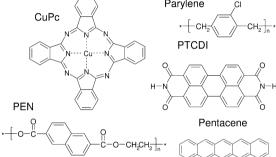

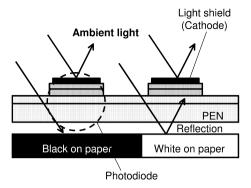

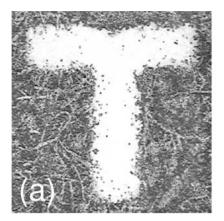

|     | 16.6                                  | Sheet Image Scanners 402                                                                                                                                                                                                                                                 |

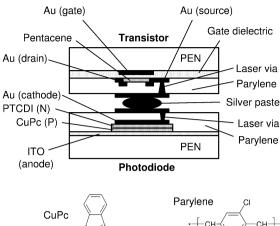

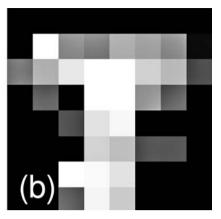

|     | 16.6<br>16.7                          | Sheet Image Scanners 402<br>Three-dimensional Integrated Circuits 405                                                                                                                                                                                                    |

|     | 16.6<br>16.7<br>16.8                  | Sheet Image Scanners 402 Three-dimensional Integrated Circuits 405 Future Prospects of Large-area Electronics 407                                                                                                                                                        |

|     | 16.6<br>16.7<br>16.8<br>16.9          | Sheet Image Scanners 402 Three-dimensional Integrated Circuits 405 Future Prospects of Large-area Electronics 407 Remaining Issues 407                                                                                                                                   |

|     | 16.6<br>16.7<br>16.8                  | Sheet Image Scanners 402 Three-dimensional Integrated Circuits 405 Future Prospects of Large-area Electronics 407 Remaining Issues 407 Conclusions 408                                                                                                                   |

|     | 16.6<br>16.7<br>16.8<br>16.9          | Sheet Image Scanners 402 Three-dimensional Integrated Circuits 405 Future Prospects of Large-area Electronics 407 Remaining Issues 407 Conclusions 408 Acknowledgments 409                                                                                               |

|     | 16.6<br>16.7<br>16.8<br>16.9          | Sheet Image Scanners 402 Three-dimensional Integrated Circuits 405 Future Prospects of Large-area Electronics 407 Remaining Issues 407 Conclusions 408                                                                                                                   |

|     | 16.6<br>16.7<br>16.8<br>16.9          | Sheet Image Scanners 402 Three-dimensional Integrated Circuits 405 Future Prospects of Large-area Electronics 407 Remaining Issues 407 Conclusions 408 Acknowledgments 409                                                                                               |

|     | 16.6<br>16.7<br>16.8<br>16.9<br>16.10 | Sheet Image Scanners 402 Three-dimensional Integrated Circuits 405 Future Prospects of Large-area Electronics 407 Remaining Issues 407 Conclusions 408 Acknowledgments 409 References 409                                                                                |

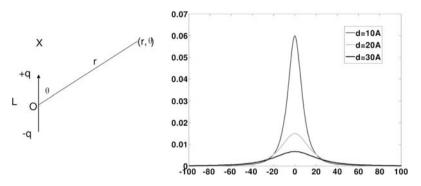

|     | 16.6<br>16.7<br>16.8<br>16.9<br>16.10 | Sheet Image Scanners 402 Three-dimensional Integrated Circuits 405 Future Prospects of Large-area Electronics 407 Remaining Issues 407 Conclusions 408 Acknowledgments 409 References 409  Organic Semiconductor-based Chemical Sensors 411                              |

|     | 16.6<br>16.7<br>16.8<br>16.9<br>16.10 | Sheet Image Scanners 402 Three-dimensional Integrated Circuits 405 Future Prospects of Large-area Electronics 407 Remaining Issues 407 Conclusions 408 Acknowledgments 409 References 409  Organic Semiconductor-based Chemical Sensors 411 Howard E. Katz and Jia Huang |

416

Index 422

Conclusion

References 419

Mechanistic Rationale

418

17.4

17.5

## **Preface**

This book is devoted to the technology of organic transistors. First reported twenty years ago, organic transistors quickly became a focus of intense research and development not only in academia, but in a rapidly increasing number of industrial laboratories. In fact, the initial reports on organic transistors originated from Japanese corporate research groups, and the first integrated circuits based on organic transistors were developed by Philips. Meanwhile, an astonishing number of university groups and non-corporate research centers have engaged in organic electronics research and have made critical contributions in many important areas such as device physics, materials chemistry, process optimization, and novel applications aspects.

For this volume, 42 authors representing 18 research groups in France, the United States, Canada, Germany, Great Britain, Austria, The Netherlands, and Japan have pooled their knowledge, experience and insights to provide a fascinating look at today's organic electronics landscape and project its future. The content of the book displays a striking balance between contributions from industry and academia, which evolved naturally in the early stages of the project. The significant number of crucial contributions from industry stands as a testament both to the progress made in developing the technology in corporate environments as well as to the continued commercial interest, while the remarkable body of work from universities and non-corporate centers is critically important to illuminate some of the fundamental problems that remain to be solved and to accelerate the advancement of a broad range of novel routes that may prove vital to the ultimate success of organic electronics.

# V Preface

As a first-time editor I am profoundly indebted to the tremendous support provided by all of the individuals involved in this project. First and foremost I want to acknowledge and thank the authors who have given so generously of their time and expertise and with their attention and responsiveness have made the editorial task both a great privilege and a smooth ride. Second I would like to express my gratitude to Bettina Bems, Martin Ottmar, Nele Denzau and Claudia Nussbeck at Wiley-VCH for giving me the opportunity to organize this book, for all the invaluable help in the editorial process, and for the wonderful experience of working with them. Finally, I want to thank all the readers for their interest in this book and hope that it is of good scientific value to them.

Stuttgart, Spring 2006

Hagen Klauk

## **Author List**

#### John E. Anthony

Department of Chemistry University of Kentucky Lexington, KY 40506-0055 USA

#### Ana Claudia Arias

Electronic Materials and Devices Laboratory Palo Alto Research Center 3333 Coyote Hill Road Palo Alto, CA 94304 USA

#### Martin Bergsmann

Hueck Folien GmbH Gewerbepark 30 4342 Baumgartenberg Austria

#### Graciela Blanchet

DuPont Central Sciences & Engineering Experimental Station E356/284 PO Box 80356 Wilmington, DE 19880 USA

# Eugenio Cantatore

Philips Research Laboratories Prof. Holstlaan 4 5656 AA Eindhoven The Netherlands

#### Michael L. Chabinyc

Electronic Materials and Devices Laboratory Palo Alto Research Center 3333 Coyote Hill Road Palo Alto, CA 94304 USA

#### Jürgen H. Daniel

Electronic Materials and Devices Laboratory Palo Alto Research Center 3333 Coyote Hill Road Palo Alto, CA 94304 USA

#### Gerwin H. Gelinck

Polymer Vision Philips Technology Incubator High Tech Campus Eindhoven 48 5656 AE Eindhoven The Netherlands

#### Marcus Halik

Department of Polymer Materials Institute of Material Science Friedrich-Alexander-Universität Erlangen-Nuremberg Martensstraße 7 91058 Erlangen Germany

#### Michael Heuken

AIXTRON AG Kackertstr. 15–17 52072 Aachen Germany

#### Gilles Horowitz

ITODYS CNRS UMR 7086 Université Denis-Diderot (Paris 7) 1 rue Guy de la Brosse 75005 Paris France

#### Jia Huang

Department of Materials Science and Engineering Johns Hopkins University 3400 North Charles Street, 102 Maryland Hall Baltimore, MD 21218 USA

#### H. Edzer A. Huitema

Polymer Vision Philips Technology Incubator High Tech Campus Eindhoven 48 5656 AE Eindhoven The Netherlands

#### Howard E. Katz

Department of Materials Science and Engineering Johns Hopkins University 3400 North Charles Street, 102 Maryland Hall Baltimore, MD 21218 USA

#### Tommie Kelley

3M Advanced Optical Solution Laboratory 260-5B-09 St. Paul, MN 55144-1000 USA

#### Hee Hyun Lee

DuPont Central Research & Development Experimental Section PO Box 80356 Wilmington, DE 19880 USA and Department of Materials Science and Engineering University of Illinois 1304 West Green Street Urbana, IL 61801 USA

#### Dago M. de Leeuw

Philips Research Laboratories Prof. Holstlaan 4 5656 AA Eindhoven The Netherlands

# Yuning Li

Materials Design and Integration Laboratory Xerox Research Centre of Canada 2660 Speakman Drive Mississauga, OT L5K 2L1 Canada

#### Pieter J. G. van Lieshout

Polymer Vision Philips Technology Incubator High Tech Campus Eindhoven 48 5656 AE Eindhoven The Netherlands

#### René Lujan

Electronic Materials and Devices Laboratory Palo Alto Research Center 3333 Coyote Hill Road Palo Alto, CA 94304 USA

#### William A. MacDonald

DuPont Teijin Films PO Box 2002 Wilton Middlesbrough, TS90 8JF UK

#### Alwin W. Marsman

Philips IP&S Prof. Holstlaan 6 5656 AA Eindhoven The Netherlands

#### Eduard J. Meijer

Philips Research Laboratories Prof. Holstlaan 4 5656 AA Eindhoven The Netherlands

#### Nico Meyer

AIXTRON AG Kackertstr. 15–17 52072 Aachen Germany

#### Shelby F. Nelson

Kodak Research Labs Eastman Kodak Company 1999 Lake Avenue Rochester, NY 14650-2102 USA

#### Beng S. Ong

Materials Design & Integration Laboratory Xerox Research Centre of Canada 2660 Speakman Drive Mississauga, OT L5K 2L1 Canada

#### Catherine Ramsdale

Plastic Logic Ltd 34 Cambridge Science Park, Milton Road Cambridge, CB4 OFX

#### Steven E. Ready

Electronic Materials and Devices Laboratory Palo Alto Research Center 3333 Coyote Hill Road Palo Alto, CA 94304 USA

#### John Rogers

Department of Materials Science and Engineering University of Illinois 1304 West Green Street Urbana, IL 61801 USA

#### Takayasu Sakurai

Center for Collaborative Research University of Tokyo 4-6-1 Komaba, Neguro-ku Tokyo 153-8505 Japan

#### Alberto Salleo

Department of Materials Science and Engineering Stanford University Stanford, Ca 94305-2205 USA

#### Christoph Sele

Cavendish Laboratory University of Cambridge J. J. Thomson Avenue Cambridge, CB3 OHE UK

#### Henning Sirringhaus

Cavendish Laboratory University of Cambridge J. J. Thomson Avenue Cambridge, CB3 OHE UK and Plastic Logic Ltd 34 Cambridge Science Park, Milton Road Cambridge, CB4 OFX UK

#### Takao Someva

Quantum-Phase Electronics Center School of Engineering University of Tokyo 7-3-1 Hongo, Bunkvo-ku Tokyo 113-8656 Japan

#### Carl J. Stonley

18 St. Leonards Drive Wollaton Nottingham, NG8 2BB UK

#### Fred J. Touwslager

Polymer Vision Philips Technology Incubator High Tech Campus Eindhoven 48 5656 AE Eindhoven The Netherlands

#### Roland Treutlein

Hueck Folien GmbH & Co. KG PO Box 1758 92607 Weiden Germany

#### Erik van Veenendaal

Polymer Vision Philips Technology Incubator High Tech Campus Eindhoven 48 5656 AE Eindhoven The Netherlands

# Timothy von Werne

Plastic Logic Ltd 34 Cambridge Science Park, Milton Road Cambridge, CB4 OFX UK

#### William Wong

Electronic Materials and Devices Laboratory Palo Alto Research Center 3333 Coyote Hill Road Palo Alto, CA 94304 USA

#### Yiliang Wu

Materials Design & Integration Laboratory Xerox Research Centre of Canada Mississauga, OT L5K 2L1 Canada

# Lisong Zhou

**Electrical Engineering Department** Pennsylvania State University 121 Electrical Engineering East University Park, PA 16802 USA

I

Introduction

#### 1

# **Organic Transistors**

Gilles Horowitz

#### 1.1 Introduction

Although the beginning of the electronics age was marked by Karl Braun's cathode ray tube (1897) and Ambrose Fleming's vacuum rectifier (1904), it was actually launched by Lee de Forest's vacuum-tube "triode" (1906); by including a "grid" between the anode and the cathode, the triode transformed the rectifier into an amplifier, thus making radio communications and long-distance telephone a reality. The vacuum triode had its limitations, however - it was fragile, rather slow, difficult to miniaturize, consumed too much energy and produced too much heat. The idea of replacing the triode with a solid-state device offering an alternative to the thermionic principle can be traced back to the mid-1920s. In October 1926, Julius Edgar Lilienfeld filled a patent describing an "apparatus for controlling the flow of an electric current between two terminals of an electronically conducting solid by establishing a third potential between said terminals" [1]. He probably never got his device to work, and his patent went into obscurity. It was not until thirty years later that this early concept could be successfully demonstrated. This was not with the celebrated Bardeen and Brattain's "point-contact" transistor (1947), nor with Shockley's bipolar transistor (1948) - both devices were based on different principles. Actually, nearly fifteen more years of material technology research were needed to finalize the silicon-silicon dioxide metal-oxidesemiconductor field-effect transistor (MOSFET) [2]. Today, MOSFETs dominate our environment; there are millions of them in the processors used in personal computers, cellular phones, and many other microelectronic devices. The success of MOSFETs actually rests on a continuous improvement in the handling of one semi-conducting material, silicon.

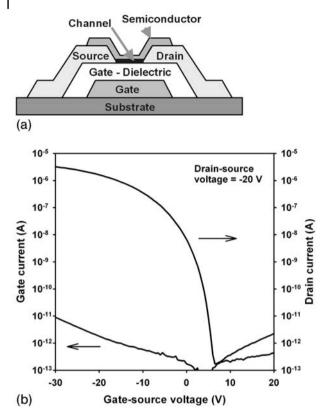

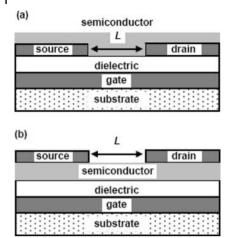

Besides their numerous technological applications, FETs have also been used as tools for studying charge transport in solid materials; this is because the device gives direct access to charge-carrier mobility. A celebrated example of such a concept is with hydrogenated amorphous silicon (a-Si:H). For this, an alternative architecture was employed, the thin-film transistor (TFT) [3], which differs from the MOSFET in that the conducting channel is induced in the accumulation regime

rather than through the formation of an inversion layer. The first a-Si:H TFTs were actually designed to measure the mobility of the material, which was at that time difficult to access by other techniques [4, 5]. It was only later that the technological importance of the device was recognized in applications in which large area is required and where single crystalline silicon can no longer be used. Today, a-Si:H TFTs play a crucial role in active-matrix liquid-crystal displays (AM-LCD).

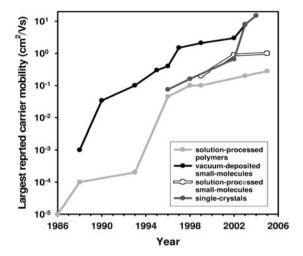

Organic semiconductors have been identified as early as the late 1940 [6]. Because they are low mobility materials, the TFT structure is well suited to these solids. Apart from a handful of isolated preliminary reports [7–9], however, work on organic thin-film transistors only emerged in the late 1980s on both polymers [10, 11] and small molecules [12, 13]. Because of the poor performance of these initial devices, interest in organic thin film transistors (OTFTs) remained limited to a small number of academic groups for nearly ten more years. During that period, much research effort was devoted to improving the charge-carrier mobility; several review papers can be consulted to learn of this quest for better materials and device structure [14–18]. It is only when the mobility of organic semiconductors approached, and even surpassed, that of amorphous silicon [19] that several industrial groups decided to embark into research programs on OTFTs.